有源晶振輸出系列終止技術的布局計劃

來源:http://netflixyz.com 作者:金洛鑫電子 2019年09月10

如今無論是在生活中還是工作中,晶體和振蕩器的身影幾乎是無處不在了,而且性能和封裝尺寸越來越合適當代產(chǎn)品的發(fā)展需求,有源晶振的分類有很多種,每一種都具備不同的功能.按照輸出方式不同,它可以分為CMOS,LVCMOS,HCMOS,HCSL,LVDS,LVPECL,削峰正弦波,方波,削波正弦波等.在產(chǎn)品性能中起到很大的作用,早已成為時鐘源或時序產(chǎn)品中,最重要的電子元器件之一.

在當今的高性能系統(tǒng)中,需要一個出色的時鐘源.隨著專用集成電路(ASIC)的速度和性能達到更高的限制,分配該時鐘源以驅(qū)動多個設備的需求變得更加困難.由于相關的快速邊沿速率,系統(tǒng)中部署的較高頻率導致長PCB跡線表現(xiàn)得像傳輸線.維護平衡系統(tǒng)需要適當?shù)慕K止技術來實現(xiàn)應用程序中的跟蹤路由.本應用筆記將重點介紹推薦的終止技術;關于輸出負載的評論,并提供一些設計師要考慮的布局指南.

傳輸線理論簡介:

通常,大多數(shù)時鐘源具有低阻抗輸出.當這些晶振用于驅(qū)動具有大阻抗的負載時,存在阻抗不匹配.根據(jù)應用條件,此阻抗不匹配會導致負載產(chǎn)生電壓反射,從而產(chǎn)生時鐘波形中的步進,振鈴以及過沖和下沖.這可能通過降低負載處的時鐘信號,錯誤的數(shù)據(jù)時鐘和產(chǎn)生更高的系統(tǒng)噪聲而導致系統(tǒng)性能不佳.

為了減少電壓反射,需要正確終止信號跡線.適當終止的設計考慮因素可以用兩個語句來概括:

1.使負載阻抗與線路阻抗相匹配

2.使源阻抗與線路阻抗匹配

對于大多數(shù)有源晶振電路設計,第一種說法是首選方法,因為它消除了返回時鐘源的反射.這樣可以減少噪音,電磁干擾(EMI)和射頻干擾(RFI).下圖顯示了阻抗不匹配對較高頻率時鐘源的影響. 常用終止技術:

如上所述,為了減少電壓反射,必須正確地終止跡線.傳輸線的四種基本端接技術是串聯(lián),并聯(lián),戴維寧和AC.

系列終止:

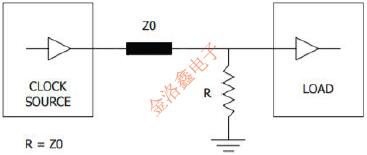

串聯(lián)終端消除了時鐘源的反射,有助于保持貼片振蕩器信號質(zhì)量.這最適合驅(qū)動少量負載的TTL器件,因為時鐘輸出阻抗小于傳輸線特性阻抗.圖1顯示了一系列終端.電阻盡可能靠近時鐘源放置.R的典型設計值為10Ω至75Ω.

圖1

R的值可以大于阻抗差,以便產(chǎn)生稍微過阻尼的狀態(tài)并且仍然消除來自時鐘源的反射.

系列終端的主要優(yōu)點是:

簡單,只需一個電阻器功耗低在驅(qū)動高容性負載時提供限流功能;這還可以通過減少接地反彈來改善抖動性能.串聯(lián)終端的主要缺點是:增加負載信號的上升和下降時間;這在某些高速應用中可能是不可接受的.不能驅(qū)動多個負載并行和戴維寧終端接下來的三種有源晶振終端技術可以提供更清晰的時鐘信號并消除負載端的反射.這些終端應盡可能靠近負載放置.

圖2描繪了并行終端.并聯(lián)終端消耗的功率最大,不建議用于低功率應用.它也可能改變占空比,因為下降沿將比上升沿更快.它比串聯(lián)終端具有一個優(yōu)點,即上升和下降時間的延遲大約是一半. 如圖3所示,戴維寧終端將比并聯(lián)終端消耗更少的功率,并且通常用于PECL應用,50Ω線路匹配至關重要.R的總值等于傳輸線的特征阻抗.如果需要過阻尼狀態(tài),則R的總值可略小于特征阻抗.戴維寧終端的主要缺點是每條線路需要兩個電阻器,并且在終端附近需要兩個電源電壓.建議不要將此端接用于TTL或CMOS電路.

圖3

AC終止:

AC端接,如圖4所示,在并聯(lián)支路中增加了一個串聯(lián)電容.由于RC時間常數(shù),電容會增加時鐘源的負載和延遲,但在穩(wěn)態(tài)條件下將消耗很少或沒有功率.通常不建議使用此終端,因為它會通過增加傳播延遲時間來降低時鐘信號的性能.為了保持有效終止,CL的值不應小于50pF.較大的CL值將允許時鐘邊沿的快速轉換,但隨著電容器值的增加,較高的電流電平將通過,從而導致有源貼片晶振功耗增加.選擇大于走線阻抗的RL值,以考慮負載輸入阻抗的泄漏.

圖4

輸出負載簡介:

應注意不要使時鐘源過載.如果使用單個時鐘源來驅(qū)動多個負載,則如果總負載超過時鐘源的驅(qū)動能力,則會發(fā)生波形劣化.過載的一些常見癥狀是波形削波,對稱不平衡,信號幅度減小以及上升和下降時間值的變化.通常隨著石英晶振頻率的增加,源驅(qū)動更高負載的能力將降低.請務必參考時鐘源規(guī)范以獲得最大負載能力.下圖顯示了時鐘源上的過載影響.

適當?shù)呢撦d條件-過載情況

通用時鐘輸出類型:

CTS時鐘振蕩器設計已開發(fā)出各種封裝選項,輸入電壓和輸出類型.HCMOS和HCMOS/TTL兼容,CTS設計目前提供“雙兼容”振蕩器,這是HCMOS輸出類型,能夠驅(qū)動TTL應用.由于轉換時間較短,這些設備固有地具有更大的過沖和欠沖.這可能不適合具有嚴格EMI要求的舊TTL設計.CTS生產(chǎn)兩種流行的HCMOS/TTL兼容時鐘振蕩器CB3/CB3LV和型號636.下圖顯示了典型的HCMOS測試負載配置和波形參數(shù). LVPECL和LVDS:

與HCMOS邏輯技術相比,CTS晶振的LVPECL和LVDS邏輯輸出設計具有許多優(yōu)勢.LVPECL和LVDS技術從正電源獲得其工作功率,從而實現(xiàn)與負載點處的HCMOS邏輯接口的必要兼容性.

這些邏輯輸出還具有:

降低系統(tǒng)抖動;由于較小的特征過渡區(qū)域更快的上升和下降時間可以提供差分輸出;減少排放必不可少的能力直接驅(qū)動50Ω傳輸線能夠在高頻下降低電源消耗CTS635型提供任何輸出類型的選項.

布局指南:

在印刷電路板布局過程中采用良好的設計實踐將最小化先前討論的有源晶振信號劣化.PCB設計的一些常見指導原則是:將時鐘源物理定位在盡可能靠近負載的位置限制時鐘信號的走線長度不要將時鐘信號路由到電路板邊緣附近盡量避免在時鐘信號路由中使用過孔.過孔會改變引起反射的走線阻抗.不要在電源和接地層上布置信號走線.

在當今的高性能系統(tǒng)中,需要一個出色的時鐘源.隨著專用集成電路(ASIC)的速度和性能達到更高的限制,分配該時鐘源以驅(qū)動多個設備的需求變得更加困難.由于相關的快速邊沿速率,系統(tǒng)中部署的較高頻率導致長PCB跡線表現(xiàn)得像傳輸線.維護平衡系統(tǒng)需要適當?shù)慕K止技術來實現(xiàn)應用程序中的跟蹤路由.本應用筆記將重點介紹推薦的終止技術;關于輸出負載的評論,并提供一些設計師要考慮的布局指南.

傳輸線理論簡介:

通常,大多數(shù)時鐘源具有低阻抗輸出.當這些晶振用于驅(qū)動具有大阻抗的負載時,存在阻抗不匹配.根據(jù)應用條件,此阻抗不匹配會導致負載產(chǎn)生電壓反射,從而產(chǎn)生時鐘波形中的步進,振鈴以及過沖和下沖.這可能通過降低負載處的時鐘信號,錯誤的數(shù)據(jù)時鐘和產(chǎn)生更高的系統(tǒng)噪聲而導致系統(tǒng)性能不佳.

為了減少電壓反射,需要正確終止信號跡線.適當終止的設計考慮因素可以用兩個語句來概括:

1.使負載阻抗與線路阻抗相匹配

2.使源阻抗與線路阻抗匹配

對于大多數(shù)有源晶振電路設計,第一種說法是首選方法,因為它消除了返回時鐘源的反射.這樣可以減少噪音,電磁干擾(EMI)和射頻干擾(RFI).下圖顯示了阻抗不匹配對較高頻率時鐘源的影響. 常用終止技術:

如上所述,為了減少電壓反射,必須正確地終止跡線.傳輸線的四種基本端接技術是串聯(lián),并聯(lián),戴維寧和AC.

系列終止:

串聯(lián)終端消除了時鐘源的反射,有助于保持貼片振蕩器信號質(zhì)量.這最適合驅(qū)動少量負載的TTL器件,因為時鐘輸出阻抗小于傳輸線特性阻抗.圖1顯示了一系列終端.電阻盡可能靠近時鐘源放置.R的典型設計值為10Ω至75Ω.

圖1

系列終端的主要優(yōu)點是:

簡單,只需一個電阻器功耗低在驅(qū)動高容性負載時提供限流功能;這還可以通過減少接地反彈來改善抖動性能.串聯(lián)終端的主要缺點是:增加負載信號的上升和下降時間;這在某些高速應用中可能是不可接受的.不能驅(qū)動多個負載并行和戴維寧終端接下來的三種有源晶振終端技術可以提供更清晰的時鐘信號并消除負載端的反射.這些終端應盡可能靠近負載放置.

圖2描繪了并行終端.并聯(lián)終端消耗的功率最大,不建議用于低功率應用.它也可能改變占空比,因為下降沿將比上升沿更快.它比串聯(lián)終端具有一個優(yōu)點,即上升和下降時間的延遲大約是一半. 如圖3所示,戴維寧終端將比并聯(lián)終端消耗更少的功率,并且通常用于PECL應用,50Ω線路匹配至關重要.R的總值等于傳輸線的特征阻抗.如果需要過阻尼狀態(tài),則R的總值可略小于特征阻抗.戴維寧終端的主要缺點是每條線路需要兩個電阻器,并且在終端附近需要兩個電源電壓.建議不要將此端接用于TTL或CMOS電路.

圖3

AC端接,如圖4所示,在并聯(lián)支路中增加了一個串聯(lián)電容.由于RC時間常數(shù),電容會增加時鐘源的負載和延遲,但在穩(wěn)態(tài)條件下將消耗很少或沒有功率.通常不建議使用此終端,因為它會通過增加傳播延遲時間來降低時鐘信號的性能.為了保持有效終止,CL的值不應小于50pF.較大的CL值將允許時鐘邊沿的快速轉換,但隨著電容器值的增加,較高的電流電平將通過,從而導致有源貼片晶振功耗增加.選擇大于走線阻抗的RL值,以考慮負載輸入阻抗的泄漏.

圖4

應注意不要使時鐘源過載.如果使用單個時鐘源來驅(qū)動多個負載,則如果總負載超過時鐘源的驅(qū)動能力,則會發(fā)生波形劣化.過載的一些常見癥狀是波形削波,對稱不平衡,信號幅度減小以及上升和下降時間值的變化.通常隨著石英晶振頻率的增加,源驅(qū)動更高負載的能力將降低.請務必參考時鐘源規(guī)范以獲得最大負載能力.下圖顯示了時鐘源上的過載影響.

適當?shù)呢撦d條件-過載情況

CTS時鐘振蕩器設計已開發(fā)出各種封裝選項,輸入電壓和輸出類型.HCMOS和HCMOS/TTL兼容,CTS設計目前提供“雙兼容”振蕩器,這是HCMOS輸出類型,能夠驅(qū)動TTL應用.由于轉換時間較短,這些設備固有地具有更大的過沖和欠沖.這可能不適合具有嚴格EMI要求的舊TTL設計.CTS生產(chǎn)兩種流行的HCMOS/TTL兼容時鐘振蕩器CB3/CB3LV和型號636.下圖顯示了典型的HCMOS測試負載配置和波形參數(shù). LVPECL和LVDS:

與HCMOS邏輯技術相比,CTS晶振的LVPECL和LVDS邏輯輸出設計具有許多優(yōu)勢.LVPECL和LVDS技術從正電源獲得其工作功率,從而實現(xiàn)與負載點處的HCMOS邏輯接口的必要兼容性.

這些邏輯輸出還具有:

降低系統(tǒng)抖動;由于較小的特征過渡區(qū)域更快的上升和下降時間可以提供差分輸出;減少排放必不可少的能力直接驅(qū)動50Ω傳輸線能夠在高頻下降低電源消耗CTS635型提供任何輸出類型的選項.

布局指南:

在印刷電路板布局過程中采用良好的設計實踐將最小化先前討論的有源晶振信號劣化.PCB設計的一些常見指導原則是:將時鐘源物理定位在盡可能靠近負載的位置限制時鐘信號的走線長度不要將時鐘信號路由到電路板邊緣附近盡量避免在時鐘信號路由中使用過孔.過孔會改變引起反射的走線阻抗.不要在電源和接地層上布置信號走線.

正在載入評論數(shù)據(jù)...

相關資訊

- [2023-06-29]-40~+105°C時的6G貼片石英晶體...

- [2020-07-16]通信網(wǎng)絡時鐘系統(tǒng)7x5mm溫補晶振...

- [2020-07-06]時鐘網(wǎng)絡與OCXO振蕩器的階層級別...

- [2020-06-22]Jauch公司專門為導航開發(fā)的新TC...

- [2020-06-06]解鎖Statek振蕩器系列產(chǎn)品的品質(zhì)...

- [2020-05-28]VV-800系列VCXO晶體振蕩器的包裝...

- [2020-04-30]獨家推薦MEMS振蕩器應用電機系統(tǒng)...

- [2020-04-25]海外各大元件供應商紛紛停工,是...

業(yè)務經(jīng)理

業(yè)務經(jīng)理 客服經(jīng)理

客服經(jīng)理